GMX<sup>™</sup> 256K BYTE STATIC RAM BOARD

User's Manual

COPYRIGHT @1983 GIMIX Inc. 1337 W. 37th Place Chicago, IL 60609 312-927-5510 \* TWX 910-221-4055

All Rights Reserved

Reproduction of this manual, in whole or part, by any means, without express written permission from GIMIX, Inc. is strictly prohibited.

GIMIX® amd GMX™ are trademarks of GIMIX, Inc. Chicago, IL 60609

#### GIMIX 256K BYTE STATIC RAM BOARD

#### **FEATURES**

- \* FULLY STATIC MEMORY does not require complicated refresh timing or clocks for data retention. Compatible with any DMA technique.

- \* GUARANTEED 2+ MHz. OPERATION uses high speed (150ns), 8Kx8 static RAMs with no wait states or clock stretching required.

- \* ADDRESSABLE in configurations to suit a variety of applications. Full 20 bit address decoding for 1M byte systems. Addressing compatible with OS-9™ GMX™ II and III, UniFLEX™, and FLEX™ with GIMIX-VDISK.

- \* LOW POWER RAM requires less than 350 ma. typical at 8V, for 256K Bytes. A Megabyte (4 boards) requires less than 1.5 Amps.

- \* NiCad BATTERY BACKUP for power-off data retention up to 300 Hrs. with a fully charged battery. (optional)

- \* LOW BUS VOLTAGE DETECTION inhibits memory access during power-up and power-down to prevent false writes to memory. (batt. vers.)

- \* WRITE-PROTECTABLE for PROM/ROM simulation and software debugging.

## CONTENTS

|         | INTRODUCTION                           | 1                     |

|---------|----------------------------------------|-----------------------|

| SECTION | 1: HARDWARE CONFIGURATION OPTIONS      | 1                     |

|         | 1-1: Bank Size Select Jumper (JA-1)    | 1<br>2<br>2<br>2<br>2 |

| SECTION | 2: ADDRESSING                          | 2                     |

|         | <pre>2-1: Base Address Selection</pre> | 3                     |

| SECTION | 3: BATTERY BACKUP                      | 5                     |

|         | 3-1: Voltage Threshold Adjustment      | 5                     |

| SECTION | 4: SPECIAL CONFIGURATIONS              |                       |

|         | Appendix A: 32K bank configuration     | 6                     |

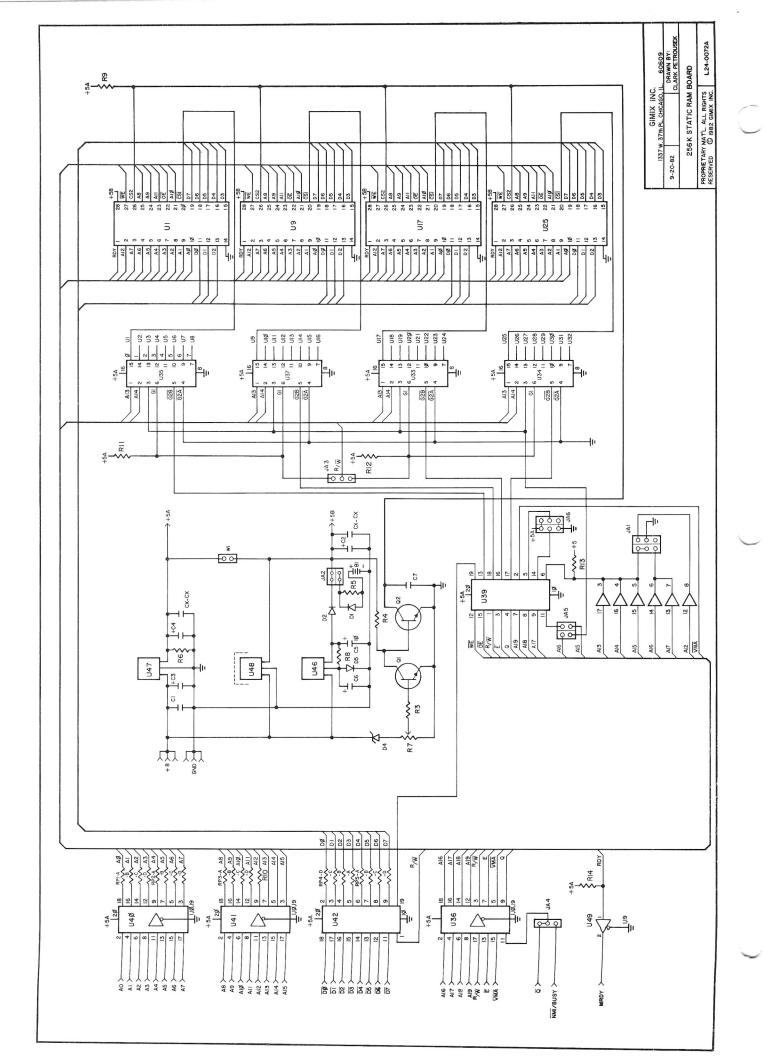

| SECTION | 5. DRAWINGS                            | 7                     |

#### \*\*\*\*\* NOTE \*\*\*\*

This manual covers both the battery backup and non-battery versions of the GIMIX 256K STATIC RAM BOARD. Except for the information on the battery backup feature the information applies to both versions. The battery and certain other components shown in the schematic are not present in the non-battery version.

### \*\*\*\* CAUTION \*\*\*\*

The battery backup versions of the board is particularly subject to damage from improper handling. See the "CAUTION" notices on pages 1 and 5.

GIMIX and GMX are trademarks of GIMIX, Inc. OS-9 is a trademark of Microware Systems Corp. FLEX and UniFLEX are trademarks of Technical Systems Consultants.

©1983 GIMIX Inc. 1337 W 37th Place Chicago, IL 60609 (312) 927-5510 \* TWX 910-221-4055

This entire manual is copyright 1983 by GIMIX Inc. Reproduction of this manual by any means, in whole or part, without express written permission from GIMIX Inc. is prohibited.

#### · INTRODUCTION

The GIMIX 256K STATIC RAM BOARD provides up to a quarter-megabyte of read/write memory on a single SS-50 board. Only four boards are required for a full megabyte of RAM; allowing more room in the mainframe for I/O and other peripherals. The board consumes less power that previous designs; which helps the system run cooler and extends the capabilities of the power supply. Using fast, 8Kx8 static RAMs and high-speed logic insures reliable performance in  $2\mbox{MHz}+\mbox{systems}$ .

#### SECTION 1: HARDWARE CONFIGURATION OPTIONS

There are several hardware jumper options which must be configured before the board is used. These jumpers determine the address of the memory and enable the write-protect and battery backup (optional) features. This section describes each of the option jumpers.

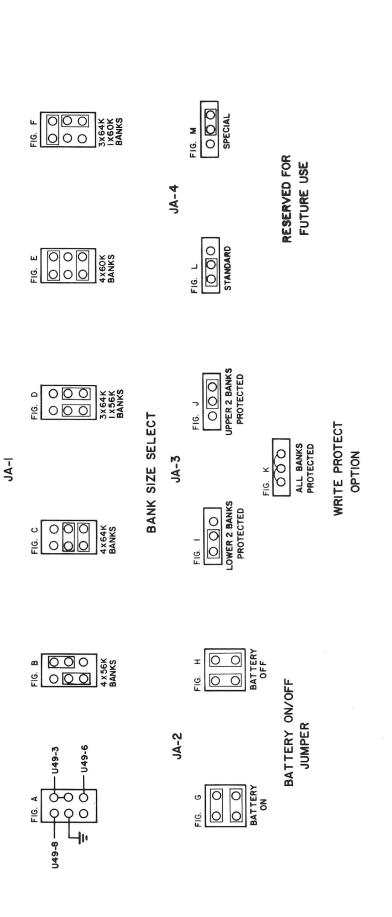

## 1-1: Bank Size Select Jumper (JA-1)

Since the board can occupy 256K of address space, it spans four "banks" of memory (the 1 Mbyte address space is divided into 16 banks of 64K each by the extended address lines A16-A19). In some system configurations, the upper 4K or 8K of some or all of the banks must be left open for the operating system and cannot contain RAM. This jumper allows parts of certain banks to be disabled. Figures A through F of the Jumper Options Drawing on page 6 show the layout of the jumper and the available options. See the section on addressing for more information.

## 1-2: Battery ON/OFF Jumper (JA-2) [battery backup version only]

This jumper enables or disables the battery backup feature on boards purchased with this option. Normally the jumper should be configured as shown in figure G of the Jumper Options Drawing on page 6 (battery ON). In this position the contents of the memory will be retained even when the system power is removed. When the jumper is in the "OFF" position (Fig. H) the battery is disconnected from the memory array.

#### \*\*\*\* CAUTION \*\*\*\*

Use caution when handling boards that have the battery backup installed. Parts of the circuit are "live" even when the board is removed from the system and the battery jumper is in the OFF position. DO NOT place the board on a conductive surface or cause shorts between the conductors on the PC board, as damage to the board and components may result. The battery jumper MUST be in the OFF position when removing ICs from the board or performing other service.

## 1-3: Write-protect Option Jumper (JA-3)

This jumper gives the user the option of write-protecting part or all of the memory on the board. Normally, with no jumpers installed at JA-3, the board operates as read/write memory. If jumpers are installed or the pins connected together in some other manner, the lower 128K, the upper 128K, or the entire board can be write-protected. Data can be read as always but the board will ignore all writes to the protected section(s). See figures I, J, and K of the Jumper Options Drawing on page 6.

The write-protect option can be enabled by using jumper blocks (as used on the other jumpers). If this feature is used often the user may wish to install a remotely mounted switch (user supplied), connected to the pins of JA-3. If installing a switch for this purpose, be sure it is rated for low current (dry) circuit use and keep wire lengths to a minimum.

## 1-4: Reserved Jumper (JA-4)

This jumper is reserved for future applications.

## 1-5: Decoding Configuration Option Jumper (JA-5)

The board is normally supplied with the standard 64K bank decoding option installed (4 banks of 64K each), and this jumper should be configured for 64K decoding as shown in figure N of the Jumper Options Drawings. A decoding option, providing 8 banks of 32K each, is available for special applications. This option requires replacement of the address decoder (U-39). Contact GIMIX for more information.

## 1-6: Base Address Select Jumper (JA-6)

This jumper selects the base address of the entire board. When using 64K pages (standard), the base address can be any one of four 256K boundaries: \$00000, \$40000, \$80000, or \$0000. The jumper configurations are shown in figures P, Q, R, and S of the Jumper Options drawings on page 6. See the section on addressing for more information.

#### SECTION 2: ADDRESSING

The board can be addressed to occupy all or part of four consecutive 64K banks, beginning on one of four possible 256K boundaries. To correctly configure the board both the base address and the size of the four banks must be determined and the jumpers (JA-1 and JA-6) set appropriately. Please note that all address references are five digit numbers, with the first digit representing the extended (bank) address.

#### 2-1: Base Address Selection

The base address of the board can be any one of four 256K boundaries in the 1M byte address space (\$00000, \$40000, \$80000, or \$0000). The base address is selected by the configuration of the jumpers at jumper area JA-6. In systems that have only one memory board, its base address MUST be \$00000 (Fig. P). This is necessary to meet the operating system's bank 0 memory requirements. If additional boards are installed, they may start at any of the remaining base addresses. Normally, the second board would be addressed at \$40000, the third at \$80000, and the fourth at \$0000. Each board must have a unique base address.

#### 2-2: Bank Size Selection

The board occupies four consecutive 64K banks of the address space, starting at the base address of the board. For example, a board set to a base address of \$00000, occupies banks \$0, \$1, \$2, and \$3. The board can be configured so that the entire 64K of each bank is occupied, or so that the upper 4 or 8K of one or all four sections is disabled. In some systems these areas MUST be disabled to prevent conflicts with the operating system PROMs. The following paragraphs describe each of these options. Note: figure references refer to the Jumper Options Drawings on page 6.

FOUR 56K BANKS (Fig. B): When this option is selected, the upper 8K (xE000-xFFFF) of all four banks is disabled. This option is used for all boards in OS-9 GMX II systems with unmodified CPU boards.

FOUR 64K BANKS (Fig. C): When this option is selected no memory is disabled. The board occupies the entire 64K of each of the four banks. This option can be used for the first three boards (\$00000, \$40000, and \$80000) in GMX III systems (0S-9 GMX III) and in 0S-9 GMX II systems where the CPU board has been modified to support 64K banks.

THREE 64K BANKS and ONE 56K BANK (Fig. D): When this option is selected only the upper 8K (\$xE000-\$xFFFF) of the last bank (highest address) is disabled. This option is used for the fourth board (base address \$C0000) in GMX III systems (OS-9 GMX III) and in OS-9 GMX II systems where the CPU board has been modified to support 64K banks.

FOUR 60K BANKS (Fig. E): When this option is selected, the upper 4K (\$xF000-\$xFFFF) of all four banks is disabled. This option is used for special applications.

THREE 64K BANKS and ONE 60K BANK (Fig. F): When this option is selected, only the upper 4K (\$xF000-\$xFFFF) of the last bank (highest address) is disabled. This option is used for special applications.

## 2-3: Standard Addressing for GIMIX Systems

The following tables show the standard address jumper (JA-1 and JA-6) configurations for GIMIX systems using from one to four 256K RAM boards.

OS-9 GMX III systems and OS-9 GMX II with modified CPU boards

| Board | JA-1<br>Fig. | JA-6<br>Fig. | 1                   | MEMORY<br>2         | ADDRESSES<br>3       | 4                   |

|-------|--------------|--------------|---------------------|---------------------|----------------------|---------------------|

| 1st   | .С           | Р            | \$00000-<br>\$0FFFF | \$10000-<br>\$1FFFF | \$20000-<br>\$2FFFF  | \$30000-<br>\$3FFFF |

| 2nd   | С            | Q            | \$40000-<br>\$4FFFF | \$50000-<br>\$5FFFF | \$60000-<br>\$6FFFF  | \$70000-<br>\$7FFFF |

| 3rd   | С            | R            | \$80000-<br>\$8FFFF | \$90000-<br>\$9FFFF | \$A0000-<br>\$AFFFF  | \$B0000-<br>\$BFFFF |

| 4th   | D            | S            | \$C0000-<br>\$CFFFF | \$D0000-<br>\$DFFFF | \$E0000-<br>•\$EFFFF | \$F0000-<br>\$FDFFF |

# OS-9 GMX II systems with unmodified CPU boards

| Board | JA-1<br>Fig. | JA-6<br>Fig. | 1                   | MEMORY<br>2         | ADDRESSES<br>3      | 4                    |          |

|-------|--------------|--------------|---------------------|---------------------|---------------------|----------------------|----------|

| 1st   | В            | , P          | \$00000-<br>\$0DFFF | \$10000-<br>\$1DFFF | \$20000-<br>\$2DFFF | \$30000-<br>\$3DFFF  |          |

| 2nd   | В            | Q            | \$40000-<br>\$4DFFF | \$50000-<br>\$5DFFF | \$60000-<br>\$6DFFF | \$70000-<br>\$7.DFFF |          |

| 3rd   | В            | R            | \$80000-<br>\$8DFFF | \$90000-<br>\$9DFFF | \$A0000-<br>\$ADFFF | \$B0000-<br>\$BDFFF  |          |

| 4th   | В            | S·           | \$C0000-<br>\$CDFFF | \$D0000-<br>\$DDFFF | \$E0000-<br>\$EDFFF | \$F0000-<br>\$FDFFF  | <b>-</b> |

The on-board Nickel-cadmium battery provides the power required to retain data in the memory when system power is removed. Data remains intact for a minimum of 300 hours with a fully charged battery. The battery is trickle charged whenever system power is applied to the board and the battery ON/OFF jumper is in the ON position. The transition between system and battery power is automatic. An adjustable unsafe voltage circuit monitors the +8V bus and inhibits memory accesses whenever the bus voltage falls below a preset safe level. This prevents false writes to the memory when the system bus is in an undefined state during power-up and down.

#### \*\*\*\* CAUTION \*\*\*\*

When the battery ON/OFF jumper (JA-2) is in the ON position, power is applied to the memory array at all times, even when the board is removed from the system. Before removing or installing parts the battery ON/OFF jumper must be placed in the OFF position to prevent possible damage to the parts. Use caution when handling the board to prevent shorting the battery terminals together or to other parts of the circuit as damage to the battery/board may occur.

## 3-1: Voltage Threshold Adjustment

The voltage at which the unsafe voltage detector activates is determined by the setting of trimmer resistor R7. This adjustment is factory set at a voltage just above the point where the on-board voltage regulator falls out of regulation, approximately 7 volts, and should not need readjustment under normal circumstances.

#### \*\*\*\*\* NOTE \*\*\*\*

In certain non-GIMIX systems the bus voltage may be too low to allow proper operation of the board. These systems will require modifications to their power supplies to provide sufficient voltage. The nominal +8V bus voltage should be somewhat above the setting of the unsafe voltage threshold to provide for normal voltage fluctuations.

## Appendix A Special Address Configuration for 32/24K banks

With decoding IC(U39) PN 12E1

In some applications it may be advantageous to address the GIMIX 256K Static RAM board in 32K pages rather than the standard 64K pages. This can only be accomplished if the board is equipped with a special version of the address decoder (IC U-39). When the special 32K decoder (part no. 12E1) is installed the following table must be used to select the board addressing.

| Board | JA-1<br>Fig.        | JA-5<br>Fig.     | JA-6<br>Fig. | . 1                                        | MEMORY<br>2                                | ADDRESSES<br>3                             | 4                                          |  |

|-------|---------------------|------------------|--------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|--------------------------------------------|--|

| 1st   | B<br>Lower<br>Banks |                  | Р            | \$00000-<br>\$07FFF<br>\$10000-<br>\$17FFF | \$20000-<br>\$27FFF<br>\$30000-<br>\$37FFF | \$40000-<br>\$47FFF<br>\$50000-<br>\$57FFF | \$60000-<br>\$67FFF<br>\$70000-<br>\$77FFF |  |

| 2nd   | B<br>Lower<br>Banks |                  | Q            | \$80000-<br>\$87FFF<br>\$90000-<br>\$97FFF | \$A0000-<br>\$A7FFF<br>\$B0000-<br>\$B7FFF | \$C0000-<br>\$C7FFF<br>\$D0000-<br>\$D7FFF | \$E0000-<br>\$E7FFF<br>\$F0000-<br>\$F7FFF |  |

| 3rd   | B<br>Upper<br>Banks | 32K †<br>\$0-\$7 | R            | \$08000-<br>\$0DFFF<br>\$18000-<br>\$1DFFF | \$28000-<br>\$2DFFF<br>\$38000-<br>\$3DFFF | \$48000-<br>\$4DFFF<br>\$58000-<br>\$5DFFF | \$68000-<br>\$6DFFF<br>\$78000-<br>\$7DFFF |  |

| 4th   | B<br>Upper<br>Banks | 32K †<br>\$8-\$F | S            | \$88000-<br>\$8DFFF<br>\$98000-<br>\$9DFFF | \$A8000-<br>\$ADFFF<br>\$B8000-<br>\$BDFFF | \$C8000-<br>\$CDFFF<br>\$D8000-<br>\$DDFFF | \$E8000-<br>\$EDFFF<br>\$F8000-<br>\$FDFFF |  |

<sup>†</sup> Note: When the upper 32K is selected, only 24K appears in each bank. The upper 8K of each bank is disabled for I/O and system ROM use.

Figure designations in the above table refer to the standard Jumper Options drawing (C24-0072A) in the 256K RAM manual.

COMPONENT LAYOUT

JA-6

000

FIG. P

BANKS \$0-\$3

OPTIONAL \*

(32K VERSION)

(64K VERSION)

DECODING CONFIGURATION

OPTION

\* NOTE: THE 32K OPTION, REQIRES A DIFFERENT DECODING &C (U-39).

0

0 STANDARD

JA-5

BANKS \$4-\$7

000 000 000 BANKS \$8-\$B

BANKS \$C-\$F

BANK ADDRESS SELECT

1337 W.37 th-PL. CHICAGO, IL. 60609 6-3-83 | DRAWN BY: CLARK PETROUSEK 256K STATIC RAM BOARD JUMPER OPTIONS GIMIX INC. PROPRIETARY MAT'L. ALL RIGHTS

RESERVED @ 1983 GIMIX INC.

C24-0072A